## Programming on Parallel Machines

Norman Matloff University of California, Davis <sup>1</sup>

<sup>1</sup> **Licensing:** This work is licensed under a Creative Commons Attribution-No Derivative Works 3.0 United States License. Copyright is retained by N. Matloff in all non-U.S. jurisdictions, but permission to use these materials in teaching is still granted, provided the authorship and licensing information here is displayed in each unit. I would appreciate being notified if you use this book for teaching, just so that I know the materials are being put to use, but this is not required.

# Contents

| 1 | Intro | oductio | n to Parallel Processing                         | 1  |

|---|-------|---------|--------------------------------------------------|----|

|   | 1.1   | Overvi  | ew: Why Use Parallel Systems?                    | 1  |

|   |       | 1.1.1   | Execution Speed                                  | 1  |

|   |       | 1.1.2   | Memory                                           | 2  |

|   | 1.2   | Paralle | Processing Hardware                              | 2  |

|   |       | 1.2.1   | Shared-Memory Systems                            | 3  |

|   |       |         | 1.2.1.1 Basic Architecture                       | 3  |

|   |       |         | 1.2.1.2 Example: SMP Systems                     | 3  |

|   |       | 1.2.2   | Message-Passing Systems                          | 4  |

|   |       |         | 1.2.2.1 Basic Architecture                       | 4  |

|   |       |         | 1.2.2.2 Example: Networks of Workstations (NOWs) | 4  |

|   |       | 1.2.3   | SIMD                                             | 5  |

|   | 1.3   | Progra  | mmer World Views                                 | 5  |

|   |       | 1.3.1   | Shared-Memory                                    | 5  |

|   |       |         | 1.3.1.1 Programmer View                          | 5  |

|   |       |         | 1.3.1.2 Example                                  | 5  |

|   |       | 1.3.2   | Message Passing                                  | 10 |

|   |       |         | 1.3.2.1 Programmer View                          | 10 |

|   |       | 1.3.3   | Example                                          | 11 |

| 2 | Sha  | red Mer | mory Parallelism                           | 15 |

|---|------|---------|--------------------------------------------|----|

|   | 2.1  | What I  | Is Shared?                                 | 15 |

|   | 2.2  | Structu | ures for Sharing                           | 16 |

|   |      | 2.2.1   | SMP Systems                                | 16 |

|   |      | 2.2.2   | NUMA Systems                               | 17 |

|   |      | 2.2.3   | NUMA Interconnect Topologies               | 18 |

|   |      |         | 2.2.3.1 Crossbar Interconnects             | 18 |

|   |      |         | 2.2.3.2 Omega (or Delta) Interconnects     | 20 |

|   |      | 2.2.4   | Comparative Analysis                       | 21 |

|   | 2.3  | Test-ar | nd-Set Type Instructions                   | 22 |

|   | 2.4  | Cache   | Issues                                     | 24 |

|   |      | 2.4.1   | Cache Coherency                            | 24 |

|   |      | 2.4.2   | Example: the MESI Cache Coherency Protocol | 26 |

|   |      | 2.4.3   | The Problem of "False Sharing"             | 28 |

|   | 2.5  | Memo    | bry-Access Consistency Policies            | 28 |

|   | 2.6  | Fetch-  | and-Add and Packet-Combining Operations    | 31 |

|   | 2.7  | Multic  | core Chips                                 | 32 |

|   | 2.8  | Illusio | on of Shared-Memory through Software       | 32 |

|   |      |         | 2.8.0.1 Software Distributed Shared Memory | 32 |

|   |      |         | 2.8.0.2 Case Study: JIAJIA                 | 35 |

| 3 | Intr | oductio | on to OpenMP                               | 39 |

|   | 3.1  | Overvi  | iew                                        | 39 |

|   | 3.2  | Runnii  | ng Example                                 | 39 |

|   |      | 3.2.1   | The Algorithm                              | 42 |

|   |      | 3.2.2   | The OpenMP parallel Pragma                 | 42 |

|   |      | 3.2.3   | Scope Issues                               | 43 |

4

|      | 3.2.4   | The OpenMP single Pragma                        | 44 |

|------|---------|-------------------------------------------------|----|

|      | 3.2.5   | The OpenMP barrier Pragma                       | 44 |

|      | 3.2.6   | Implicit Barriers                               | 44 |

|      | 3.2.7   | The OpenMP critical Pragma                      | 45 |

| 3.3  | The O   | penMP for Pragma                                | 45 |

|      | 3.3.1   | Basic Example                                   | 45 |

|      | 3.3.2   | Controlling the Partitioning of Work to Threads | 48 |

|      | 3.3.3   | The OpenMP reduction Clause                     | 49 |

| 3.4  | Other   | OpenMP Synchronization Issues                   | 50 |

|      | 3.4.1   | The OpenMP atomic Clause                        | 50 |

|      | 3.4.2   | Memory Consistency and the flush Pragma         | 51 |

| 3.5  | Comp    | iling, Running and Debugging OpenMP Code        | 52 |

|      | 3.5.1   | Compiling                                       | 52 |

|      | 3.5.2   | Running                                         | 52 |

|      | 3.5.3   | Debugging                                       | 52 |

| 3.6  | Combi   | ining Work-Sharing Constructs                   | 53 |

| 3.7  | Perfor  | mance                                           | 53 |

|      | 3.7.1   | The Effect of Problem Size                      | 53 |

|      | 3.7.2   | Some Fine Tuning                                | 54 |

|      | 3.7.3   | OpenMP Internals                                | 58 |

| 3.8  | The R   | est of OpenMP                                   | 58 |

| Intr | oductio | n to GPU Programming with CUDA                  | 59 |

|      |         |                                                 |    |

| 4.1  |         | iew                                             | 59 |

| 4.2  |         |                                                 | 60 |

|      | 4.2.1   | Processing Units                                | 60 |

|      | 4.2.2   | Memory Structure                                | 61 |

|   |                       | 4.2.3 Thread Management                                       | 1 |  |  |

|---|-----------------------|---------------------------------------------------------------|---|--|--|

|   | 4.3                   | Software Structure                                            | 1 |  |  |

|   |                       | 4.3.1 Sample Program                                          | 2 |  |  |

|   |                       | 4.3.2 Threads Hierarchy                                       | 4 |  |  |

|   |                       | 4.3.3 Memory Placement                                        | 5 |  |  |

|   |                       | 4.3.4 What's NOT There                                        | 5 |  |  |

|   | 4.4                   | Synchronization                                               | 6 |  |  |

|   | 4.5                   | Performance Issues                                            | 6 |  |  |

|   | 4.6                   | CUBLAS                                                        | 6 |  |  |

|   | 4.7                   | Hardware Requirements, Installation, Compilation, Debugging 6 | 6 |  |  |

| 5 | Mes                   | sage Passing Systems 6                                        | 9 |  |  |

|   | 5.1                   | Overview                                                      | 9 |  |  |

|   | 5.2                   | A Historical Example: Hypercubes                              | 0 |  |  |

|   |                       | 5.2.0.0.1 Definitions                                         | 0 |  |  |

|   | 5.3                   | Networks of Workstations (NOWs)                               | 2 |  |  |

|   |                       | 5.3.1 The Network Is Literally the Weakest Link               | 2 |  |  |

|   |                       | 5.3.2 Other Issues                                            | 3 |  |  |

|   | 5.4                   | Parallelizing Serial Code Via Hidden Message-Passing          | 3 |  |  |

|   |                       | 5.4.1 One Solution: Piggyback on MPI                          | 3 |  |  |

|   |                       | 5.4.2 Another Solution: MapReduce                             | 4 |  |  |

| 6 | Intro                 | oduction to MPI 7                                             | 7 |  |  |

|   | 6.1                   | Overview                                                      | 7 |  |  |

|   |                       | 6.1.1 History                                                 | 7 |  |  |

|   |                       | 6.1.2 Structure and Execution                                 | 8 |  |  |

|   |                       | 6.1.3 Implementations                                         | 8 |  |  |

|   | 0.1.5 Implementations |                                                               |   |  |  |

|     | 6.1.4  | Performa   | ance Issues                         | . 78 |

|-----|--------|------------|-------------------------------------|------|

| 6.2 | Runnii | ng Exampl  | le                                  | . 79 |

|     | 6.2.1  | The Algo   | orithm                              | . 79 |

|     | 6.2.2  | The Code   | e                                   | . 79 |

|     | 6.2.3  | Introduct  | tion to MPI APIs                    | . 83 |

|     |        | 6.2.3.1    | MPI_Init() and MPI_Finalize()       | . 83 |

|     |        | 6.2.3.2    | MPI_Comm_size() and MPI_Comm_rank() | . 83 |

|     |        | 6.2.3.3    | MPI_Send()                          | . 83 |

|     |        | 6.2.3.4    | MPI_Recv()                          | . 84 |

| 6.3 | Collec | tive Comn  | nunications                         | . 85 |

|     | 6.3.1  | Example    | ,                                   | . 85 |

|     | 6.3.2  | MPI_Bca    | ast()                               | . 87 |

|     |        | 6.3.2.1    | MPI_Reduce()/MPI_Allreduce()        | . 88 |

|     |        | 6.3.2.2    | MPI_Gather()/MPI_Allgather()        | . 89 |

|     |        | 6.3.2.3    | The MPI_Scatter()                   | . 90 |

|     |        | 6.3.2.4    | The MPI_Barrier()                   | . 90 |

|     | 6.3.3  | Creating   | Communicators                       | . 90 |

| 6.4 | Buffer | ing, Synch | nrony and Related Issues            | . 90 |

|     | 6.4.1  | Buffering  | g, Etc                              | . 91 |

|     | 6.4.2  | Safety .   |                                     | . 92 |

|     | 6.4.3  | Living D   | Dangerously                         | . 92 |

|     | 6.4.4  | Safe Exc   | change Operations                   | . 93 |

| 6.5 | Use of | MPI from   | Other Languages                     | . 93 |

|     | 6.5.1  | Python: j  | руМРІ                               | . 93 |

|     | 6.5.2  | R          |                                     | . 95 |

|     |        | 6.5.2.1    | Rmpi                                | . 95 |

|     |        | 6.5.2.2    | Snow                                | . 97 |

v

| 7 | Intr | duction to Parallel Matrix Operations     | 101 |

|---|------|-------------------------------------------|-----|

|   | 7.1  | Overview                                  | 101 |

|   | 7.2  | Message-Passing Setting                   | 102 |

|   | 7.3  | Partitioned Matrices                      | 102 |

|   | 7.4  | Matrix Multiplication                     | 103 |

|   |      | 7.4.1 Fox's Algorithm                     | 104 |

|   |      | 7.4.2 Performance Issues                  | 105 |

|   |      | 7.4.3 Finding Powers of Matrices          | 105 |

|   | 7.5  | Solving Systems of Linear Equations       | 105 |

|   |      | 7.5.1 Gaussian Elimination                | 106 |

|   |      | 7.5.2 Iterative Methods                   | 107 |

|   |      | 7.5.2.1 The Jacobi Algorithm              | 107 |

|   |      | 7.5.2.2 The Gauss-Seidel Algorithm        | 107 |

|   | 7.6  | The Shared-Memory Case                    | 108 |

| 8 | Para | llel Combinitorial Algorithms             | 109 |

|   | 8.1  | Overview                                  | 109 |

|   | 8.2  | The 8 Queens Problem                      | 109 |

|   | 8.3  | The 8-Square Puzzle Problem               | 110 |

|   | 8.4  | Itemset Analysis in Data Mining           | 112 |

|   |      | 8.4.1 What Is It?                         | 112 |

|   |      | 8.4.2 The Market Basket Problem           | 113 |

|   |      | 8.4.3 Serial Algorithms                   | 113 |

|   |      | 8.4.4 Parallelizing the Apriori Algorithm | 114 |

| 9 | Intr | duction to Parallel Sorting               | 115 |

|   | 9.1  | Quicksort                                 | 115 |

|    |      | 9.1.1                                                                                              | Shared-Memory Quicksort                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6                                                                                              |

|----|------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|    |      |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

|    |      | 9.1.2                                                                                              | Hyperquicksort                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                                                                              |

|    | 9.2  | Merges                                                                                             | orts                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                                                                              |

|    |      | 9.2.1                                                                                              | Sequential Form                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                                                                                              |

|    |      | 9.2.2                                                                                              | Shared-Memory Mergesort                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                              |

|    |      | 9.2.3                                                                                              | Message Passing Mergesort on a Tree Topology                                                                                                                                                                                                                                                                                                                                                                                                                             | 8                                                                                              |

|    |      | 9.2.4                                                                                              | Compare-Exchange Operations                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                                                              |

|    |      | 9.2.5                                                                                              | Bitonic Mergesort                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9                                                                                              |

|    | 9.3  | The Bu                                                                                             | bble Sort and Its Cousins                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21                                                                                             |

|    |      | 9.3.1                                                                                              | The Much-Maligned Bubble Sort                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21                                                                                             |

|    |      | 9.3.2                                                                                              | A Popular Variant: Odd-Even Transposition                                                                                                                                                                                                                                                                                                                                                                                                                                | 21                                                                                             |

|    | 9.4  | Shears                                                                                             | ort                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22                                                                                             |

|    | 9.5  | Bucket                                                                                             | Sort with Sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                                                             |

|    |      |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

| 10 | Para | llel Cor                                                                                           | nnutation of Fourier Series, with an Introduction to Parallel Imaging 12                                                                                                                                                                                                                                                                                                                                                                                                 | 25                                                                                             |

| 10 |      |                                                                                                    | nputation of Fourier Series, with an Introduction to Parallel Imaging                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                |

| 10 |      | Genera                                                                                             | l Principles                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25                                                                                             |

| 10 |      | Genera                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                                                                             |

| 10 |      | Genera<br>10.1.1                                                                                   | l Principles                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25<br>25                                                                                       |

| 10 | 10.1 | Genera<br>10.1.1<br>10.1.2                                                                         | I Principles   12     One-Dimensional Fourier Series   12                                                                                                                                                                                                                                                                                                                                                                                                                | 25<br>25<br>29                                                                                 |

| 10 | 10.1 | Genera<br>10.1.1<br>10.1.2<br>Discret                                                              | I Principles       12         One-Dimensional Fourier Series       12         Two-Dimensional Fourier Series       12                                                                                                                                                                                                                                                                                                                                                    | 25<br>25<br>29<br>29                                                                           |

| 10 | 10.1 | Genera<br>10.1.1<br>10.1.2<br>Discret<br>10.2.1                                                    | I Principles       12         One-Dimensional Fourier Series       12         Two-Dimensional Fourier Series       12         e Fourier Transforms       12                                                                                                                                                                                                                                                                                                              | 25<br>25<br>29<br>29<br>30                                                                     |

| 10 | 10.1 | Genera<br>10.1.1<br>10.1.2<br>Discret<br>10.2.1<br>10.2.2                                          | I Principles       12         One-Dimensional Fourier Series       12         Two-Dimensional Fourier Series       12         e Fourier Transforms       12         One-Dimensional Data       13                                                                                                                                                                                                                                                                        | 25<br>25<br>29<br>29<br>30                                                                     |

| 10 | 10.1 | Genera<br>10.1.1<br>10.1.2<br>Discret<br>10.2.1<br>10.2.2                                          | 1 Principles       12         One-Dimensional Fourier Series       12         Two-Dimensional Fourier Series       12         e Fourier Transforms       12         One-Dimensional Data       13         Two-Dimensional Data       13         I Computation of Discrete Fourier Transforms       13                                                                                                                                                                    | 25<br>25<br>29<br>30<br>31<br>31                                                               |

| 10 | 10.1 | Genera<br>10.1.1<br>10.1.2<br>Discret<br>10.2.1<br>10.2.2<br>Paralle<br>10.3.1                     | 1 Principles       12         One-Dimensional Fourier Series       12         Two-Dimensional Fourier Series       12         e Fourier Transforms       12         One-Dimensional Data       13         Two-Dimensional Data       13         I Computation of Discrete Fourier Transforms       13                                                                                                                                                                    | <ol> <li>25</li> <li>25</li> <li>29</li> <li>29</li> <li>30</li> <li>31</li> <li>31</li> </ol> |

| 10 | 10.1 | Genera<br>10.1.1<br>10.1.2<br>Discret<br>10.2.1<br>10.2.2<br>Paralle<br>10.3.1<br>10.3.2           | 1 Principles       12         One-Dimensional Fourier Series       12         Two-Dimensional Fourier Series       12         e Fourier Transforms       12         One-Dimensional Data       12         Two-Dimensional Data       13         The Fast Fourier Transform       13                              | 25<br>25<br>29<br>29<br>30<br>31<br>31<br>31<br>32                                             |

| 10 | 10.1 | Genera<br>10.1.1<br>10.1.2<br>Discret<br>10.2.1<br>10.2.2<br>Paralle<br>10.3.1<br>10.3.2<br>10.3.3 | 1 Principles       12         One-Dimensional Fourier Series       12         Two-Dimensional Fourier Series       12         e Fourier Transforms       12         One-Dimensional Data       12         Two-Dimensional Data       13         A Matrix Approach       13 | 25<br>29<br>29<br>30<br>31<br>31<br>31<br>32<br>32                                             |

|      | 10.4.1 Smoothing                                                                        |

|------|-----------------------------------------------------------------------------------------|

|      | 10.4.2 Edge Detection                                                                   |

| 10.5 | The Cosine Transform                                                                    |

| 10.6 | Keeping the Pixel Intensities in the Proper Range                                       |

| 10.7 | Does the Function g() Really Have to Be Repeating?                                      |

| 10.8 | Vector Space Issues (optional section)                                                  |

| 10.9 | Bandwidth: How to Read the San Francisco Chronicle Business Page (optional section) 138 |

## **Chapter 1**

# **Introduction to Parallel Processing**

Parallel machines provide a wonderful opportunity for applications with large computational requirements. Effective use of these machines, though, requires a keen understanding of how they work. This chapter provides an overview.

## 1.1 Overview: Why Use Parallel Systems?

## 1.1.1 Execution Speed

There is an ever-increasing appetite among some types of computer users for faster and faster machines. This was epitomized in a statement by Steve Jobs, founder/CEO of Apple and Pixar. He noted that when he was at Apple in the 1980s, he was always worried that some other company would come out with a faster machine than his. But now at Pixar, whose graphics work requires extremely fast computers, he is always hoping someone produces faster machines, so that he can use them!

A major source of speedup is the parallelizing of operations. Parallel operations can be either withinprocessor, such as with pipelining or having several ALUs within a processor, or between-processor, in which many processor work on different parts of a problem in parallel. Our focus here is on betweenprocessor operations.

For example, the Registrar's Office at UC Davis uses shared-memory multiprocessors for processing its on-line registration work. Online registration involves an enormous amount of database computation. In order to handle this computation reasonably quickly, the program partitions the work to be done, assigning different portions of the database to different processors. The database field has contributed greatly to the commercial success of large shared-memory machines.

As the Pixar example shows, highly computation-intensive applications like computer graphics also have a

need for these fast parallel computers. No one wants to wait hours just to generate a single image, and the use of parallel processing machines can speed things up considerably. For example, consider **ray tracing** operations. Here our code follows the path of a ray of light in a scene, accounting for reflection and absorbtion of the light by various objects. Suppose the image is to consist of 1,000 rows of pixels, with 1,000 pixels per row. In order to attack this problem in a parallel processing manner with, say, 25 processors, we could divide the image into 25 squares of size 200x200, and have each processor do the computations for its square.

Note, though, that it may be much more challenging than this implies. First of all, the computation will need some communication between the processors, which hinders performance if it is not done carefully. Second, if one really wants good speedup, one may need to take into account the fact that some squares require more computation work than others. More on this below.

In this setting you need the program to run as fast as possible. Thus, in order to write good parallel processing software, you must have a good knowledge of the underlying hardware. You must find clever tricks for **load balancing,** i.e. keeping all the processors busy as much as possible. In the graphics ray-tracing application, for instance, suppose a ray is coming from the "northeast" section of the image, and is reflected by a solid object. Then the ray won't reach some of the "southwest" portions of the image, which then means that the processors assigned to those portions will not have any work to do which is associated with this ray. What we need to do is then try to give these processors some other work to do; the more they are idle, the slower our system will be.

#### 1.1.2 Memory

Yes, execution speed is the reason that comes to most people's minds when the subject of parallel processing comes up. But in many applications, an equally important consideration is memory capacity. Parallel processing application often tend to use huge amounts of memory, and in many cases the amount of memory needed is more than can fit on one machine. If we have many machines working together, especially in the message-passing settings described below, we can accommodate the large memory needs.

## **1.2 Parallel Processing Hardware**

This is not a hardware course, but since the goal of using parallel hardware is speed, the efficiency of our code is a major issue. That in turn means that we need a good understanding of the underlying hardware that we are programming. In this section, we give an overview of parallel hardware.

#### 1.2. PARALLEL PROCESSING HARDWARE

#### 1.2.1 Shared-Memory Systems

#### **1.2.1.1 Basic Architecture**

Here many CPUs share the same physical memory. This kind of architecture is sometimes called MIMD, standing for Multiple Instruction (different CPUs are working independently, and thus typically are executing different instructions at any given instant), Multiple Data (different CPUs are generally accessing different memory locations at any given time).

Until recently, shared-memory systems cost hundreds of thousands of dollars and were affordable only by large companies, such as in the insurance and banking industries. The high-end machines are indeed still quite expensive, but now **dual-core** machines, in which two CPUs share a common memory, are common-place in the home.

#### 1.2.1.2 Example: SMP Systems

A Symmetric Multiprocessor (SMP) system has the following structure:

Here and below:

- The Ps are processors, e.g. off-the-shelf chips such as Pentiums.

- The Ms are **memory modules**. These are physically separate objects, e.g. separate boards of memory chips. It is typical that there will be the same number of memory modules as processors. In the shared-memory case, the memory modules collectively form the entire shared address space, but with the addresses being assigned to the memory modules in one of two ways:

– (a)

High-order interleaving. Here consecutive addresses are in the <u>same M</u> (except at boundaries). For example, suppose for simplicity that our memory consists of addresses 0 through 1023, and that there are four Ms. Then M0 would contain addresses 0-255, M1 would have 256-511, M2 would have 512-767, and M3 would have 768-1023.

We need 10 bits for addresses (since  $1024 = 2^{10}$ ). The two most-significant bits would be used to select the module number (since  $4 = 2^2$ ); hence the term *high-order* in the name of this design. The remaining eight bits are used to select the word within a module.

– (b)

Low-order interleaving. Here consecutive addresses are in consecutive memory modules (except when we get to the right end). In the example above, if we used low-order interleaving, then address 0 would be in M0, 1 would be in M1, 2 would be in M2, 3 would be in M3, 4 would be back in M0, 5 in M1, and so on.

Here the two least-significant bits are used to determine the module number.

- To make sure only one processor uses the bus at a time, standard bus arbitration signals and/or arbitration devices are used.

- There may also be **coherent caches**, which we will discuss later.

## 1.2.2 Message-Passing Systems

#### 1.2.2.1 Basic Architecture

Here we have a number of independent CPUs, each with its own independent memory. The various processors communicate with each other via networks of some kind.

## **1.2.2.2** Example: Networks of Workstations (NOWs)

Large shared-memory multiprocessor systems are still very expensive. A major alternative today is networks of workstations (NOWs). Here one purchases a set of commodity PCs and networks them for use as parallel processing systems. The PCs are of course individual machines, capable of the usual uniprocessor (or now multiprocessor) applications, but by networking them together and using parallel-processing software environments, we can form very powerful parallel systems.

The networking does result in a significant loss of performance. This will be discussed in a later unit. But even without these techniques, the price/performance ratio in NOW is much superior in many applications to that of shared-memory hardware.

One factor which can be key to the success of a NOW is the use of a fast network, fast both in terms of hardware and network protocol. Ordinary Ethernet and TCP/IP are fine for the applications envisioned by the original designers of the Internet, e.g. e-mail and file transfer, but is slow in the NOW context. A good network for a NOW is, for instance, Infiniband.

NOWs have become so popular that there are now "recipes" on how to build them for the specific purpose of parallel processing. The term **Beowulf** come to mean a cluster of PCs, usually with a fast network connecting them, used for parallel processing. Software packages such as ROCKS (http://www.rocksclusters.org/wordpress/) have been developed to make it easy to set up and administer such systems.

#### 1.3. PROGRAMMER WORLD VIEWS

#### 1.2.3 SIMD

In contrast to MIMD systems, processors in SIMD—Single Instruction, Multiple Data—systems execute in lockstep. At any given time, all processors are executing the same machine instruction on different data.

## **1.3 Programmer World Views**

To explain the two paradigms, we will use the term **nodes**, where roughly speaking one node corresponds to one processor, and use the following example:

Suppose we wish to multiply an nx1 vector X by an nxn matrix A, putting the product in an nx1 vector Y, and we have p processors to share the work.

#### **1.3.1 Shared-Memory**

#### **1.3.1.1 Programmer View**

In the shared-memory paradigm, the arrays for A, X and Y would be held in common by all nodes. If for instance node 2 were to execute

Y[3] = 12;

and then node 15 were to subsequently execute

print("%d\n",Y[3]);

then the outputted value from the latter would be 12.

#### 1.3.1.2 Example

Today, programming on shared-memory multiprocessors is typically done via **threading**. (Or, as we will see in other units, by higher-level code that runs threads underneath.) A **thread** is similar to a **process** in an operating system (OS), but with much less overhead. Threaded applications have become quite popular in even uniprocessor systems, and Unix,<sup>1</sup> Windows, Python, Java and Perl all support threaded programming.

<sup>&</sup>lt;sup>1</sup>Here and below, the term *Unix* includes Linux.

In the typical implementation, a thread is a special case of an OS process. One important difference is that the various threads of a program share memory. (One can arrange for processes to share memory too in some OSs, but they don't do so by default.)

On a uniprocessor system, the threads of a program take turns executing, so that there is only an illusion of parallelism. But on a multiprocessor system, one can genuinely have threads running in parallel.

One of the most popular threads systems is Pthreads, whose name is short for POSIX threads. POSIX is a Unix standard, and the Pthreads system was designed to standardize threads programming on Unix. It has since been ported to other platforms.

Following is an example of Pthreads programming, in which we determine the number of prime numbers in a certain range. Read the comments at the top of the file for details; the threads operations will be explained presently.

```

// PrimesThreads.c

1

2

// threads-based program to find the number of primes between 2 and n;

3

// uses the Sieve of Eratosthenes, deleting all multiples of 2, all

4

// multiples of 3, all multiples of 5, etc.

5

6

// for illustration purposes only; NOT claimed to be efficient

7

8

9

// Unix compilation: gcc -g -o primesthreads PrimesThreads.c -lpthread -lm

10

11

// usage: primesthreads n num_threads

12

#include <stdio.h>

13

14

#include <math.h>

15

#include <pthread.h> // required for threads usage

16

#define MAX N 10000000

17

18

#define MAX_THREADS 25

19

20

// shared variables

int nthreads, // number of threads (not counting main())

21

n, // range to check for primeness

22

prime[MAX_N+1], // in the end, prime[i] = 1 if i prime, else 0

23

nextbase; // next sieve multiplier to be used

24

// lock for the shared variable nextbase

25

26

pthread_mutex_t nextbaselock = PTHREAD_MUTEX_INITIALIZER;

// ID structs for the threads

27

28 pthread_t id[MAX_THREADS];

29

// "crosses out" all odd multiples of k

30

31

void crossout(int k)

32 { int i;

33

for (i = 3; i*k <= n; i += 2) {

prime[i \star k] = 0;

34

35

}

}

36

37

38

// each thread runs this routine

39

void *worker(int tn) // tn is the thread number (0,1,...)

```

6

#### 1.3. PROGRAMMER WORLD VIEWS

```

40

{ int lim, base,

work = 0; // amount of work done by this thread

41

42

// no need to check multipliers bigger than sqrt(n)

lim = sqrt(n);

43

44

do {

// get next sieve multiplier, avoiding duplication across threads

45

// lock the lock

46

47

pthread_mutex_lock(&nextbaselock);

base = nextbase;

48

49

nextbase += 2;

// unlock

50

51

pthread_mutex_unlock(&nextbaselock);

52

if (base <= lim) {

53

// don't bother crossing out if base known composite

54

if (prime[base])

{

55

crossout (base);

work++; // log work done by this thread

56

57

}

58

}

59

else return work;

} while (1);

60

61

}

62

63

main(int argc, char **argv)

{ int nprimes, // number of primes found

64

i,work;

65

n = atoi(argv[1]);

66

nthreads = atoi(argv[2]);

67

68

// mark all even numbers nonprime, and the rest "prime until

69

// shown otherwise"

for (i = 3; i <= n; i++) {

70

71

if (i%2 == 0) prime[i] = 0;

else prime[i] = 1;

72

73

}

nextbase = 3;

74

75

// get threads started

76

for (i = 0; i < nthreads; i++) {</pre>

// this call says to create a thread, record its ID in the array

77

78

// id, and get the thread started executing the function worker(),

// passing the argument i to that function

79

80

pthread_create(&id[i],NULL,worker,i);

}

81

82

83

// barrier, to wait for all done

for (i = 0; i < nthreads; i++) {</pre>

84

// this call said to wait until thread number id[i] finishes

85

// execution, and to assign the return value of that thread to our

86

87

// local variable work here

88

pthread_join(id[i],&work);

printf("%d values of base done\n",work);

89

90

}

91

// report results

92

93

nprimes = 1;

for (i = 3; i <= n; i++)

94

95

if (prime[i]) {

nprimes++;

96

97

}

```

```

98 printf("the number of primes found was %d\n",nprimes);

99

100 }

```

To make our discussion concrete, suppose we are running this program with two threads. Suppose also the both threads are running simultaneously most of the time. This will occur if they aren't competing for turns with other big threads, say if there are no other big threads, or more generally if the number of other big threads is less than or equal to the number of processors minus two.

Note the global variables:

```

int nthreads, // number of threads (not counting main())

n, // range to check for primeness

prime[MAX_N+1], // in the end, prime[i] = 1 if i prime, else 0

nextbase; // next sieve multiplier to be used

pthread_mutex_t nextbaselock = PTHREAD_MUTEX_INITIALIZER;

pthread_t id[MAX_THREADS];

```

This will require some adjustment for those who've been taught that global variables are "evil." All communication between threads is via global variables, so if they are evil, they are a necessary evil. Personally I think the stern admonitions against global variables is overblown anyway. See <a href="http://heather.cs.ucdavis.edu/~matloff/globals.html">http://heather.cs.ucdavis.edu/~matloff/globals.html</a>.

As mentioned earlier, the globals are shared by all processors.<sup>2</sup> If one processor, for instance, assigns the value 0 to **prime[35]** in the function **crossout()**, then that variable will have the value 0 when accessed by any of the other processors as well. On the other hand, local variables have different values at each processor; for instance, the variable **i** in that function has a different value at each processor.

Note that in the statement

pthread\_mutex\_t nextbaselock = PTHREAD\_MUTEX\_INITIALIZER;

the right-hand side is not a constant. It is a macro call, and is thus something which is executed.

In the code

```

pthread_mutex_lock(&nextbaselock);

base = nextbase

nextbase += 2

pthread_mutex_unlock(&nextbaselock);

```

we see a **critical section** operation which is typical in shared-memory programming. In this context here, it means that we cannot allow more than one thread to execute

<sup>&</sup>lt;sup>2</sup>Technically, we should say "shared by all threads" here, as a given thread does not always execute on the same processor, but at any instant in time each executing thread is at some processor, so the statement is all right.

#### 1.3. PROGRAMMER WORLD VIEWS

```

base = nextbase;

nextbase += 2;

```

at the same time. The calls to **pthread\_mutex\_lock()** and **pthread\_mutex\_unlock()** ensure this. If thread A is currently executing inside the critical section and thread B tries to lock the lock by calling **pthread\_mutex\_lock()**, the call will block until thread B executes **pthread\_mutex\_unlock()**.

Here is why this is so important: Say currently **nextbase** has the value 11. What we want to happen is that the next thread to read **nextbase** will "cross out" all multiples of 11. But if we allow two threads to execute the critical section at the same time, the following may occur:

- thread A reads **nextbase**, setting its value of **base** to 11

- thread B reads **nextbase**, setting its value of **base** to 11

- thread A adds 2 to nextbase, so that nextbase becomes 13

- thread B adds 2 to nextbase, so that nextbase becomes 15

Two problems would then occur:

- Both threads would do "crossing out" of multiples of 11, duplicating work and thus slowing down execution speed.

- We will never "cross out" multiples of 13.

Thus the lock is crucial to the correct (and speedy) execution of the program.

Note that these problems could occur either on a uniprocessor or multiprocessor system. In the uniprocessor case, thread A's turn might end right after it reads **nextbase**, followed by a turn by B which executes that same instruction. In the multiprocessor case, A and B could literally be running simultaneously, but still with the action by B coming an instant after A.

This problem frequently arises in parallel database systems. For instance, consider an airline reservation system. If a flight has only one seat left, we want to avoid giving it to two different customers who might be talking to two agents at the same time. The lines of code in which the seat is finally assigned (the **commit** phase, in database terminology) is then a critical section.

A critical section is always a potential bottlement in a parallel program, because its code is serial instead of parallel. In our program here, we may get better performance by having each thread work on, say, five values of **nextbase** at a time. Our line

```

nextbase += 2;

```

would become

nextbase += 10;

That would mean that any given thread would need to go through the critical section only one-fifth as often, thus greatly reducing overhead. On the other hand, near the end of the run, this may result in some threads being idle while other threads still have a lot of work to do.

Note the **barrier**:

```

for (i = 0; i < nthreads; i++) {

pthread_join(id[i],&work);

printf("%d values of base done\n",work);

}</pre>

```

A barrier is a point in the code that all threads must reach before continuing. In this case, a barrier is needed in order to prevent premature execution of the later code

```

for (i = 3; i <= n; i++)

if (prime[i])    {

nprimes++;

}</pre>

```

which would result in possibly wrong output if we start counting primes before some threads are done.

The **pthread\_join**() function actually causes the given thread to exit, so that we then "join" the thread that created it, i.e. **main**(). Thus some may argue that this is not really a true barrier.

Barriers are very common in shared-memory programming, and will be discussed in more detail in a later unit.

#### **1.3.2** Message Passing

#### 1.3.2.1 Programmer View

By contrast, in the message-passing paradigm, all nodes would have <u>separate</u> copies of A, X and Y. In this case, in our example above, in order for node 2 to send this new value of Y[3] to node 15, it would have to execute some special function, which would be something like

```

send(15,12,"Y[3]");

```

#### 1.3. PROGRAMMER WORLD VIEWS

and node 15 would have to execute some kind of receive() function.

The conventional wisdom is that the shared-memory paradigm is much easier to program in than the message-passing paradigm. The latter, however, may be easier to implement, and in some settings may have greater speed.

#### 1.3.3 Example

Here we use the MPI system, with our hardware being a NOW.

MPI is a popular public-domain set of interface functions, callable from C/C++, to do message passing. We are again counting primes, though in this case using a **pipelining** method. It is similar to hardware pipelines, but in this case it is done in software, and each "stage" in the pipe is a different computer.

The program is self-documenting, via the comments.

```

/* MPI sample program: NOT INTENDED TO BE EFFICIENT as a prime

2

finder, either in algorithm or implementation

3

4

5

MPI (Message Passing Interface) is a popular package using

the "message passing" paradigm for communicating between

6

processors in parallel applications; as the name implies,

7

processors communicate by passing messages using "send" and

8

"receive" functions

9

10

11

finds and reports the number of primes less than or equal to N

12

uses a pipeline approach: node 0 looks at all the odd numbers

13

(i.e. has already done filtering out of multiples of 2) and

14

15

filters out those that are multiples of 3, passing the rest

16

to node 1; node 1 filters out the multiples of 5, passing

17

the rest to node 2; in this simple example, we just have node

18

2 filter out all the rest and then report the number of primes

19

note that we should NOT have a node run through all numbers

20

before passing them on to the next node, since we would then

21

have no parallelism at all; on the other hand, passing on just

22

23

one number at a time isn't efficient either, due to the high

overhead of sending a message if it is a network (tens of

24

25

microseconds until the first bit reaches the wire, due to

software delay); thus efficiency would be greatly improved if

26

each node saved up a chunk of numbers before passing them to

27

28

the next node */

29

30

// this include file is mandatory

#include <mpi.h>

31

32

#define MAX N 100000

33

34

#define PIPE_MSG 0 // type of message containing a number to

35

be checked

36

#define END_MSG 1 // type of message indicating no more data will

```

```

be coming

37

38

39

int NNodes, /* number of nodes in computation*/

N, /* find all primes from 2 to N */

40

41

Me, /* my node number */

ToCheck; /* current number to check for passing on to next node;

42

43

stylistically this might be nicer as a local in

44

Node*(), but I have placed it here to dramatize

the fact that the globals are NOT shared among

45

the nodes */

46

47

48

double T1, T2; /* start and finish times */

49

50

Init (Argc, Argv)

51

int Argc; char **Argv;

52

{ int DebugWait;

53

54

55

N = atoi(Argv[1]);

56

DebugWait = atoi(Argv[2]);

57

58

/* this loop is here to synchronize all nodes for debugging;

if DebugWait is specified as 1 on the command line, all nodes

59

60

wait here until the debugging programmer starts GDB at all

61

nodes and within GDB sets DebugWait to 0 to then proceed */

while (DebugWait) ;

62

63

/* mandatory to begin any MPI program */

64

65

MPI_Init(&Argc, &Argv);

66

/* puts the number of nodes in NNodes */

67

68

MPI_Comm_size(MPI_COMM_WORLD, &NNodes);

/* puts the node number of this node in Me */

69

MPI_Comm_rank(MPI_COMM_WORLD, &Me);

70

71

72

/* OK, get started; first record current time in T1 */

73

if (Me == 2) T1 = MPI_Wtime();

74

}

75

Node0()

76

77

78

{ int I, Dummy,

Error; /* not checked in this example */

for (I = 1; I <= N/2; I++) {</pre>

79

80

ToCheck = 2 * I + 1;

81

if (ToCheck > N) break;

82

/* MPI_Send -- send a message

83

84

parameters:

85

pointer to place where message is to be drawn from

number of items in message

86

item type

87

88

destination node

message type ("tag") programmer-defined

89

90

node group number (in this case all nodes) \star/

91

if (ToCheck % 3 > 0)

92

Error = MPI_Send(&ToCheck,1,MPI_INT,1,PIPE_MSG,MPI_COMM_WORLD);

93

}

94

Error = MPI_Send(&Dummy, 1, MPI_INT, 1, END_MSG, MPI_COMM_WORLD);

```

#### 1.3. PROGRAMMER WORLD VIEWS

```

95

}

96

97

Nodel()

98

99

{ int Error, /* not checked in this example */

100

Dummy;

MPI_Status Status; /* see below */

101

102

while (1) {

103

/* MPI_Recv -- receive a message

104

105

parameters:

pointer to place to store message

106

107

number of items in message (see notes on

this at the end of this file)

108

109

item type

110

accept message from which node(s)

message type ("tag"), programmer-defined (in this

111

112

case any type)

113

node group number (in this case all nodes)

114

status (see notes on this at the end of this file) */

Error = MPI_Recv(&ToCheck,1,MPI_INT,0,MPI_ANY_TAG,

115

116

MPI_COMM_WORLD,&Status);

if (Status.MPI_TAG == END_MSG) break;

117

118

if (ToCheck % 5 > 0)

119

Error = MPI_Send(&ToCheck,1,MPI_INT,2,PIPE_MSG,MPI_COMM_WORLD);

120

}

121

/* now send our end-of-data signal, which is conveyed in the

message type, not the message (we have a dummy message just

122

123

as a placeholder */

Error = MPI_Send(&Dummy,1,MPI_INT,2,END_MSG,MPI_COMM_WORLD);

124

}

125

126

Node2()

127

128

{ int ToCheck, /* current number to check from Node 0 */

129

Error, /* not checked in this example */

130

131

PrimeCount, I, IsComposite;

MPI_Status Status; /* see below */

132

133

PrimeCount = 3; /* must account for the primes 2, 3 and 5, which

134

135

won't be detected below */

136

while (1) {

137

Error = MPI_Recv(&ToCheck, 1, MPI_INT, 1, MPI_ANY_TAG,

138

MPI_COMM_WORLD, & Status);

if (Status.MPI_TAG == END_MSG) break;

139

IsComposite = 0;

140

for (I = 7; I*I <= ToCheck; I += 2)</pre>

141

142

if (ToCheck % I == 0) {

143

IsComposite = 1;

144

break;

}

145

if (!IsComposite) PrimeCount++;

146

147

}

148

/* check the time again, and subtract to find run time */

T2 = MPI Wtime();

149

150

printf("elapsed time = %f\n",(float)(T2-T1));

151

/* print results */

printf("number of primes = %d\n",PrimeCount);

152

```

```

153

}

154

155

main(argc,argv)

int argc; char **argv;

156

157

158

{ Init(argc,argv);

/* note: instead of having a switch statement, we could write

159

160

three different programs, each running on a different node */

switch (Me) {

161

case 0: Node0();

162

break;

163

case 1: Node1();

164

165

break;

case 2: Node2();

166

167

};

168

/* mandatory for all MPI programs */

MPI_Finalize();

169

170

}

171

172

/\star explanation of "number of items" and "status" arguments at the end

of MPI_Recv():

173

174

when receiving a message you must anticipate the longest possible

175

176

message, but the actual received message may be much shorter than

177

this; you can call the MPI_Get_count() function on the status

argument to find out how many items were actually received

178

179

the status argument will be a pointer to a struct, containing the

180

node number, message type and error status of the received

181

182

message

183

184

say our last parameter is Status; then Status.MPI_SOURCE

will contain the number of the sending node, and

185

Status.MPI_TAG will contain the message type; these are

186

important if used MPI_ANY_SOURCE or MPI_ANY_TAG in our

187

node or tag fields but still have to know who sent the

188

189

message or what kind it is \star/

```

The set of machines can be heterogeneous, but MPI "translates" for you automatically. If say one node has a big-endian CPU and another has a little-endian CPU, MPI will do the proper conversion.

## Chapter 2

# **Shared Memory Parallelism**

Shared-memory programming is considered by many in the parallel processing community as being the clearest of the various parallel paradigms available.

## 2.1 What Is Shared?

The term **shared memory** means that the processors all share a common address space. Say this is occurring at the hardware level, and we are using Intel Pentium CPUs. Suppose processor P3 issues the instruction

movl 200, %eabx

which reads memory location 200 and places the result in the EAX register in the CPU. If processor P4 does the same, they both will be referring to the same physical memory cell. In non-shared-memory machines, each processor has its own private memory, and each one will then have its own location 200, completely independent of the locations 200 at the other processors' memories.

Say a program contains a global variable **X** and a local variable **Y** on share-memory hardware (and we use shared-memory software). If for example the compiler assigns location 200 to the variable **X**, i.e. &X = 200, then the point is that all of the processors will have that variable in common, because any processor which issues a memory operation on location 200 will access the same physical memory cell.

On the other hand, each processor will have its own separate run-time stack. All of the stacks are in shared memory, but they will be accessed separately, since each CPU has a different value in its SP (Stack Pointer) register. Thus each processor will have its own independent copy of the local variable Y.

To make the meaning of "shared memory" more concrete, suppose we have a bus-based system, with all the processors and memory attached to the bus. Let us compare the above variables **X** and **Y** here. Suppose

again that the compiler assigns  $\mathbf{X}$  to memory location 200. Then in the machine language code for the program, every reference to  $\mathbf{X}$  will be there as 200. Every time an instruction that writes to  $\mathbf{X}$  is executed by a CPU, that CPU will put 200 into its Memory Address Register (MAR), from which the 200 flows out on the address lines in the bus, and goes to memory. This will happen in the same way no matter which CPU it is. Thus the same physical memory location will end up being accessed, no matter which CPU generated the reference.

By contrast, say the compiler assigns **Y** to something like ESP+8, the third item on the stack. (It is 8 bytes past the word pointed to by the stack pointer, ESP.) Each CPU will have its own current value for ESP, so the stacks of the various CPUs will be separate. Note that the stacks <u>will</u> be in the physical shared memory, and thus P3, say, could theoretically access P8's stack, say if there were an erroneous pointer value. But even that would not occur if we are using virtual memory and thus have protections against this.

## 2.2 Structures for Sharing

## 2.2.1 SMP Systems

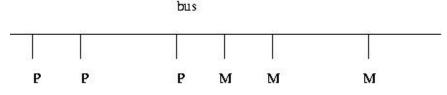

A Symmetric Multiprocessor (SMP) system has the following structure:

|   |   | bus |   |   |   |  |

|---|---|-----|---|---|---|--|

|   |   |     |   |   | 1 |  |

| P | P | Р   | М | М | М |  |

Here and below:

- The Ps are processors, e.g. off-the-shelf chips such as Pentiums.

- The Ms are **memory modules**. These are physically separate objects, e.g. separate boards of memory chips. It is typical that there will be the same number of Ms as Ps, but it does not have to be this way. In the shared-memory case, the Ms collectively form the entire shared address space, but with the addresses being assigned to the Ms in one of two ways:

- (a)

High-order interleaving. Here consecutive addresses are in the <u>same M</u> (except at boundaries). For example, suppose for simplicity that our memory consists of addresses 0 through 1023, and that there are four Ms. Then M0 would contain addresses 0-255, M1 would have 256-511, M2 would have 512-767, and M3 would have 768-1023.

- (b)

Low-order interleaving. Here consecutive addresses are in consecutive M's (except when we get to the right end). In the example above, if we used low-order interleaving, then address 0 would be in M0, 1 would be in M1, 2 would be in M2, 3 would be in M3, 4 would be back in M0, 5 in M1, and so on.

- To make sure only one P uses the bus at a time, standard bus arbitration signals and/or arbitration devices are used.

- There may also be coherent caches, which we will discuss later.

#### 2.2.2 NUMA Systems

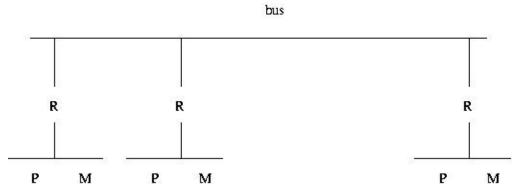

In a **Nonuniform Memory Access** (NUMA) architecture, each CPU has a memory module physically next to it, and these processor/memory (P/M) pairs are connected by some kind of network.

Here is a simple version:

Each P/M/R set here is called a **processing element** (PE). Note that each PE has its own local bus, and is also connected to the global bus via R, the router.

Suppose for example that P3 needs to access location 200, and suppose that high-order interleaving is used. If location 200 is in M3, then P3's request is satisfied by the local bus.<sup>1</sup> On the other hand, suppose location 200 is in M8. Then the R3 will notice this, and put the request on the global bus, where it will be seen by R8, which will then copy the request to the local bus at PE8, where the request will be satisfied. (E.g. if it was a read request, then the response will go back from M8 to R8 to the global bus to R3 to P3.)

It should be obvious now where NUMA gets its name. P8 will have much faster access to M8 than P3 will to M8, if none of the buses is currently in use—and if say the global bus is currently in use, P3 will have to wait a long time to get what it wants from M8.

<sup>&</sup>lt;sup>1</sup>This sounds similar to the concept of a cache. However, it is very different. A cache contains a local copy of some data stored elsewhere. Here it is the data itself, not a copy, which is being stored locally.

Today almost all high-end MIMD systems are NUMAs. One of the attractive features of NUMA is that by good programming we can exploit the nonuniformity. In matrix problems, for example, we can write our program so that, for example, P8 usually works on those rows of the matrix which are stored in M8, P3 usually works on those rows of the matrix which are stored in M3, etc. In order to do this, we need to make use of the C language's & address operator, and have some knowledge of the memory hardware structure, i.e. the interleaving.

## 2.2.3 NUMA Interconnect Topologies

The problem with a bus connection, of course, is that there is only one pathway for communication, and thus only one processor can access memory at the same time. If one has more than, say, two dozen processors are on the bus, the bus becomes saturated, even if traffic-reducing methods such as adding caches are used. Thus multipathway topologies are used for all but the smallest systems. In this section we look at two alternatives to a bus topology.

#### 2.2.3.1 Crossbar Interconnects

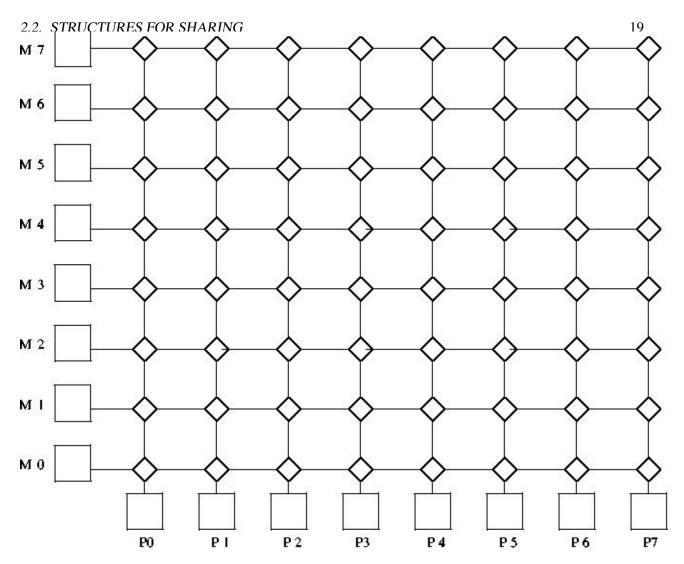

Consider a shared-memory system with n processors and n memory modules. Then a crossbar connection would provide  $n^2$  pathways. E.g. for n = 8:

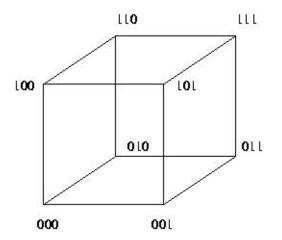

Generally serial communication is used from node to node, with a packet containing information on both source and destination address. E.g. if P2 wants to read from M5, the source and destination will be 3-bit strings in the packet, coded as 010 and 101, respectively. The packet will also contain bits which specify which word within the module we wish to access, and bits which specify whether we wish to do a read or a write. In the latter case, additional bits are used to specify the value to be written.

Each diamond-shaped node has two inputs (bottom and right) and two outputs (left and top), with buffers at the two inputs. If a buffer fills, there are two design options: (a) Have the node from which the input comes block at that output. (b) Have the node from which the input comes discard the packet, and retry later, possibly outputting some other packet for now. If the packets at the heads of the two buffers both need to go out the same output, the one (say) from the bottom input will be given priority.

There could also be a return network of the same type, with this one being memory  $\rightarrow$  processor, to return

the result of the read requests.<sup>2</sup>

Another version of this is also possible. It is not shown here, but the difference would be that at the bottom edge we would have the PEi and at the left edge the memory modules Mi would be replaced by lines which wrap back around to PEi, similar to the Omega network shown below.

Crossbar switches are too expensive for large-scale systems, but are useful in some small systems. The 16-CPU Sun Microsystems Enterprise 10000 system includes a 16x16 crossbar.

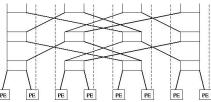

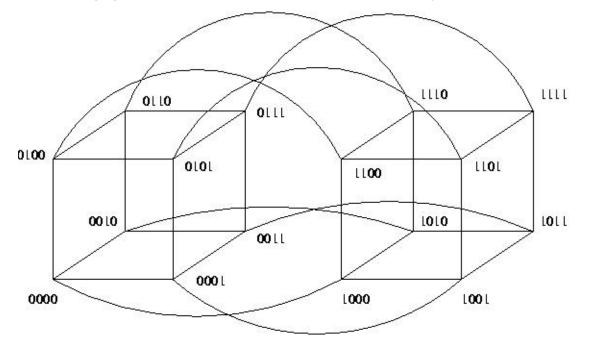

#### 2.2.3.2 Omega (or Delta) Interconnects

These are multistage networks similar to crossbars, but with fewer paths. Here is an example of a NUMA 8x8 system:

Recall that each PE is a processor/memory pair. PE3, for instance, consists of P3 and M3.

Note the fact that at the third stage of the network (top of picture), the outputs are routed back to the PEs, each of which consists of a processor and a memory module.<sup>3</sup>

At each network node (the nodes are the three rows of rectangles), the output routing is done by destination bit. Let's number the stages here 0, 1 and 2, starting from the bottom stage, number the nodes within a stage 0, 1, 2 and 3 from left to right, number the PEs from 0 to 7, left to right, and number the bit positions in a destination address 0, 1 and 2, starting from the most significant bit. Then at stage i, bit i of the destination address is used to determine routing, with a 0 meaning routing out the left output, and 1 meaning the right one.

Say P2 wishes to read from M5. It sends a read-request packet, including 5 = 101 as its destination address, to the switch in stage 0, node 1. Since the first bit of 101 is 1, that means that this switch will route the packet out its right-hand output, sending it to the switch in stage 1, node 3. The latter switch will look at the next bit in 101, a 0, and thus route the packet out its left output, to the switch in stage 2, node 2. Finally, that switch will look at the last bit, a 1, and output out its right-hand output, sending it to PE5, as desired. M5 will process the read request, and send a packet back to PE2, along the same

Again, if two packets at a node want to go out the same output, one must get priority (let's say it is the one

<sup>&</sup>lt;sup>2</sup>For safety's sake, i.e. fault tolerance, even writes are typically acknowledged in multiprocessor systems.

<sup>&</sup>lt;sup>3</sup>The picture may be cut off somewhat at the top and left edges. The upper-right output of the rectangle in the top row, leftmost position should connect to the dashed line which leads down to the second PE from the left. Similarly, the upper-left output of that same rectangle is a dashed lined, possibly invisible in your picture, leading down to the leftmost PE.

#### 2.2. STRUCTURES FOR SHARING

from the left input).

Here is how the more general case of  $N = 2^n$  PEs works. Again number the rows of switches, and switches within a row, as above. So,  $S_{ij}$  will denote the switch in the i-th row from the bottom and j-th column from the left (starting our numbering with 0 in both cases). Row i will have a total of N input ports  $I_{ik}$  and N output ports  $O_{ik}$ , where k = 0 corresponds to the leftmost of the N in each case. Then if row i is not the last row (i < n - 1),  $O_{ik}$  will be connected to  $I_{jm}$ , where j = i+1 and

$$m = (2k + |(2k)/N|) \mod N$$

(2.1)

If row i is the last row, then  $O_{ik}$  will be connected to, PE k.

#### 2.2.4 Comparative Analysis

In the world of parallel architectures, a key criterion for a proposed feature is **scalability**, meaning how well the feature performs as we go to larger and larger systems. Let n be the system size, either the number of processors and memory modules, or the number of PEs. Then we are interested in how fast the latency, bandwidth and cost grow with n:

| criterion | bus  | Omega          | crossbar |  |

|-----------|------|----------------|----------|--|

| latency   | O(1) | $O(\log_2 n)$  | O(n)     |  |

| bandwidth | O(1) | O(n)           | O(n)     |  |

| cost      | O(1) | $O(n\log_2 n)$ | $O(n^2)$ |  |

Let us see where these expressions come from, beginning with a bus: No matter how large n is, the time to get from, say, a processor to a memory module will be the same, thus O(1). Similarly, no matter how large n is, only one communication can occur at a time, thus again O(1).<sup>4</sup>

Again, we are interested only in "O()" measures, because we are only interested in growth rates as the system size n grows. For instance, if the system size doubles, the cost of a crossbar will quadruple; the  $O(n^2)$  cost measure tells us this, with any multiplicative constant being irrelevant.

For Omega networks, it is clear that  $log_2n$  network rows are needed, hence the latency value given. Also, each row will have n/2 switches, so the number of network nodes will be  $O(n log_2n)$ . This figure then gives the cost (in terms of switches, the main expense here). It also gives the bandwidth, since the maximum number of simultaneous transmissions will occur when all switches are sending at once.

Similar considerations hold for the crossbar case.

<sup>&</sup>lt;sup>4</sup> Note that the '1' in "O(1)" does not refer to the fact that only one communication can occur at a time. If we had, for example, a two-bus system, the bandwidth would still be O(1), since multiplicative constants do not matter. What O(1) means, again, is that as n grows, the bandwidth stays at a multiple of 1, i.e. stays constant.

The crossbar's big advantage is that it is guaranteed that n packets can be sent simultaneously, providing they are to distinct destinations.